从零开始制作FPGA基GPU图形加速器实现方案

一、引言

在现代计算中,图形处理已成为不可或缺的一部分,无论是游戏、设计还是科学计算,GPU都扮演着至关重要的角色。然而,传统的GPU成本高且难以定制。随着FPGA技术的快速发展,我们可以利用FPGA来构建自己的GPU,实现灵活且高效的图形处理。本文将详细介绍如何从零开始制作一个基于FPGA的图形加速器。

二、问题分析

核心问题:如何利用FPGA设计一个图形加速器? 问题分析:

- 硬件资源:FPGA具有丰富的逻辑单元和可编程互联,适合构建复杂的图形处理流水线。

- 架构设计:需要理解GPU的基本架构,如顶点处理、像素处理和纹理映射等模块。

- 编程实现:FPGA的编程通常使用硬件描述语言(HDL),如VHDL或Verilog,同时可能需要高层次综合(HLS)工具来简化设计。

三、解决方案

1. FPGA与GPU基础

1.1 FPGA简介

FPGA是一种半定制电路,用户可以通过编程来配置其内部逻辑和连接。它提供了高度的灵活性和可重配置性,非常适合用于快速原型开发和特定应用领域的硬件加速。

1.2 GPU架构概述

GPU的主要功能包括顶点处理、像素处理和纹理映射等。顶点处理负责将3D顶点转换为2D屏幕坐标;像素处理则对转换后的像素进行着色和光照计算;纹理映射则用于在渲染对象上应用纹理。

2. 图形加速器设计

2.1 架构设计

- 顶点处理单元:负责顶点坐标的变换和投影。

- 像素处理单元:对像素进行着色和光照计算。

- 纹理映射单元:负责纹理的读取和应用。

- 内存管理单元:管理帧缓冲区和纹理内存等。

2.2 HDL实现

- 顶点处理单元:使用HDL描述顶点坐标的变换和投影过程,包括矩阵乘法、裁剪和透视投影等。

- 像素处理单元:实现着色器和光照模型,使用HDL描述着色算法和光照计算。

- 纹理映射单元:设计纹理读取和插值算法,利用HDL实现纹理内存的访问和控制。

- 内存管理单元:设计内存控制器和地址映射,确保数据在FPGA和内存之间的高效传输。

2.3 HLS工具辅助

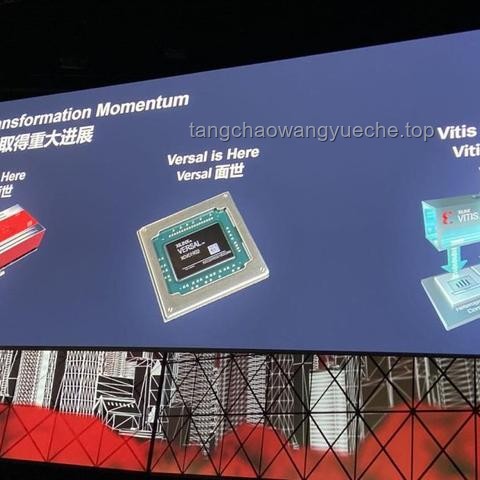

使用高层次综合(HLS)工具,如Vivado HLS或Xilinx Vitis HLS,可以将C/C++代码转换为HDL代码,简化设计过程。HLS工具可以自动处理部分硬件优化和代码生成工作,提高开发效率。

3. 验证与测试

3.1 功能验证

使用仿真工具对设计的图形加速器进行功能验证,确保各个模块能够正确工作。通过输入不同的顶点和纹理数据,检查输出是否符合预期。

3.2 性能评估

对设计的图形加速器进行性能测试,包括处理速度、内存带宽和功耗等指标。通过与其他GPU进行比较,评估设计的优劣。

3.3 硬件调试

在FPGA开发板上进行硬件调试,使用示波器、逻辑分析仪等工具检查信号波形和时序。通过调试,发现并解决硬件设计中的错误和缺陷。

4. 优化与改进

4.1 资源优化

根据功能验证和性能测试的结果,对设计进行优化,减少资源消耗并提高性能。例如,通过优化算法和数据路径,减少逻辑单元和内存的使用。

4.2 模块化设计

采用模块化设计思想,将图形加速器划分为多个独立的模块,便于维护和扩展。每个模块可以独立进行设计和测试,提高开发效率。

4.3 可重构性

利用FPGA的可重构性,设计可重构的图形加速器。通过重新配置FPGA内部逻辑和连接,实现不同图形处理任务的加速。这可以提高硬件资源的利用率和灵活性。

四、实施步骤

- 确定需求:明确图形加速器的应用场景和功能需求。

- 架构设计:根据需求设计图形加速器的架构,包括顶点处理、像素处理和纹理映射等模块。

- HDL实现:使用HDL描述各个模块的功能和连接关系,编写相应的代码。

- 功能验证:使用仿真工具对设计进行功能验证,确保各个模块能够正确工作。

- 性能评估:对设计进行性能测试,评估处理速度、内存带宽和功耗等指标。

- 硬件调试:在FPGA开发板上进行硬件调试,发现并解决硬件设计中的错误和缺陷。

- 优化与改进:根据测试结果对设计进行优化和改进,提高性能和资源利用率。

五、预防建议与后续措施

- 预防建议:

- 在设计初期进行充分的需求分析,确保设计的图形加速器能够满足应用场景的需求。

- 在HDL实现过程中,注意代码的可读性和可维护性,便于后续调试和优化。

- 在硬件调试过程中,记录详细的调试信息和数据,以便在出现问题时能够快速定位和解决。

- 后续措施:

- 对设计进行持续的优化和改进,提高性能和资源利用率。

- 关注FPGA和GPU技术的最新发展动态,及时将新技术应用到设计中。

- 与其他开发者交流和分享经验,共同推动FPGA在图形处理领域的应用和发展。

六、Q&A

Q1:为什么选择FPGA来实现图形加速器? A1:FPGA具有高度的灵活性和可重配置性,可以根据需求快速定制硬件加速器。同时,FPGA具有丰富的逻辑单元和可编程互联,适合构建复杂的图形处理流水线。 Q2:HDL和HLS的区别是什么? A2:HDL是硬件描述语言,用于直接描述硬件电路的功能和连接关系。而HLS是高层次综合工具,可以将C/C++代码转换为HDL代码,简化设计过程并提高开发效率。 Q3:在硬件调试过程中遇到问题时如何解决? A3:在硬件调试过程中遇到问题时,可以使用示波器、逻辑分析仪等工具检查信号波形和时序。同时,根据调试信息和数据,逐步排查和定位问题所在,并进行相应的修改和优化。 通过本文的介绍,读者可以了解到如何从零开始利用FPGA制作一个属于自己的GPU图形加速器。从FPGA与GPU的基础知识到图形加速器的设计、实现、验证与优化,本文提供了详细的解决方案和实施步骤。希望读者能够掌握FPGA在图形处理领域的应用,并设计出高效且灵活的图形加速器。

文章展示了有见地的从零开始制作fpga基gpu图形加速器实现方案技术的最新进展,特别是提高性能和资源利用率这一创新点很值得关注。

从技术角度看,文章对hdl实现的解析很精准,尤其是专业的hdl实现部分的技术细节很有参考价值。